常见问题

产品推荐

常见问题

用突发脉冲器准确分析脉冲抗扰度

- 发布时间:2017-09-14 09:38:52

本文重点分析电子系统抗干扰路径时的物理问题。详细请下载:如何用突发脉冲发生器准确分析脉冲抗扰度?

一、引言

今天,在最先进的电子电路中找到故障正变得越来越难。除了更加复杂(并且因此一些高得多的潜在故障源),小机械尺寸让开发人员越来越难查明故障。下面是北京海洋兴业科技股份有限公司进行测量的例子。

二、任务

一个新的控制单元是干扰发生器抗扰度试验检查的对象。该控制单元电路板包括液晶显示器(+控制器)、μC(142引脚TQFP)、FPGA(100引脚TQFP)、接口模块、无源器件(如SMD 0603)和各种控制元件(旋转编码器、按钮、开关)。此外,在电路板承载的USB插座,连接器用于将随后由发生器和电源输入来产生的电压。由于成本原因,电路板被设计成具有200微米特征尺寸的双层系统。没有连续的GND层。该总线/线放在两个层次。控制单元向发生器单元的接近导致高抗干扰要求。

根据DIN EN 61000-4-2,功能故障发生在第一次ESD测试中。干扰脉冲(接触放电)连接到电路板的接地系统后,微控制器出现故障,通过跳动信号故障和定格显示变得明显。这种故障发生在不同的电压(2.4kV-4kV)取决于静电枪的位置(连接点和角)。显然抗扰水平必须提高。

三、耦合机制

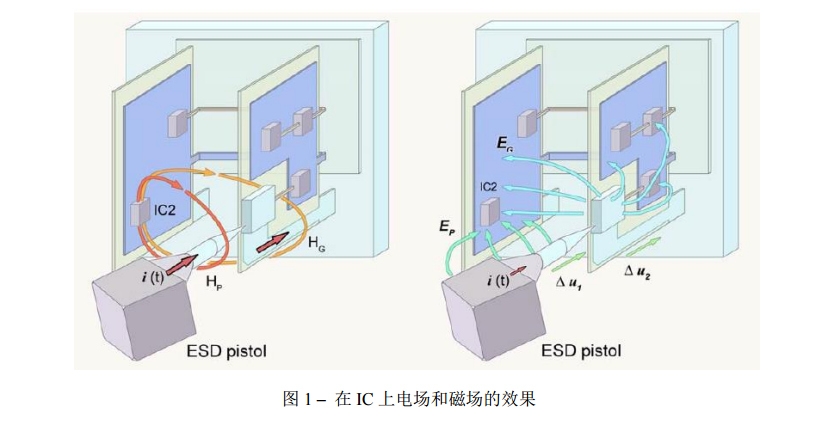

如图1所示是两种电电位耦合机制,通过该干扰可能到达电路板重要区域:磁耦合和电耦合。

当使用ESD静电枪耦合扰动到模块时,区别在:磁耦合期间,干扰电流流过电路板,并产生磁性,这反过来又可能在导体回路感应电压。这些电压可能导致两种不同类型的问题:感应电压既可以视为由该电路的输入逻辑信号,又可视为它驱动扰动电流,这会在控制电路的其它部分引起问题。

电耦合也可引起干扰。电场电容耦合到电路板的线路网络或组件。所得位移电流可能反过来以两种不同的方式影响系统:位移电流可能导致在电阻器上的电压降(反抗VSS或VDD),这再次被认为是一个逻辑信号,或在类似于磁耦合引起的电路其他部分感应电压。

干扰必须被施加到选择的各个线路(例如,在总线系统)和/或它们的通孔或单个IC引脚以查明易敏感模块组件。在微米范围内的电路和特征尺寸的一体化的上述高层导致对干扰源的机械分辨率越来越高的要求。

由于功能故障和抗扰水平知道,合适的可能性必须找到以提高系统的抗干扰性能。在合规测试中,故障范围可能缩小到控制器。但它仍然必须确定它的精确引脚是完全负责事故。这是绝对必要的,因为没有适当的反制措施(阻塞IC引脚,掩盖易敏感线)本来可以有效地采取。

一种类似ESD干扰不得不被单独地应用到每个引脚来识别易敏感线/ IC管脚。ESD静电枪不能再使用有以下几个原因:1、对于单个IC引脚,这些脉冲太强,这很容易损坏电路。2、由ESD静电枪发出的场可以影响电路的其他部分,从而阻碍显著具体的故障定位。3、机械尺寸使它几乎是不可能的连接到个别引脚无短路邻近的引脚。4、由于线密度,有受限接入到地面系统周围的电路使得难以连接到基准线。

四、路径

E或B场源常常用于局部注入干扰。但是,在目前的情况下其选择性是不充分的,并且使它们更小似乎是不明智的。这将大大减少在E场源的电极和相应的电路板结构/元件包之间的耦合电容,以致于所得的干扰脉冲不足以产生被之前注意到的故障。

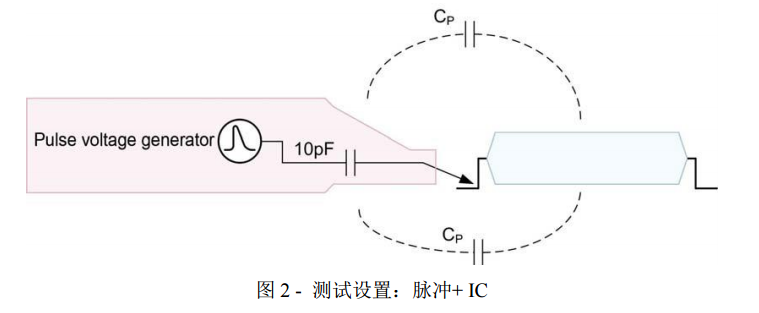

开发一种新的干扰发生器来避免这个问题。它产生边沿陡峭的干扰脉冲(1.2kV/1.8

ns上升时间),它可以通过内部电容(10

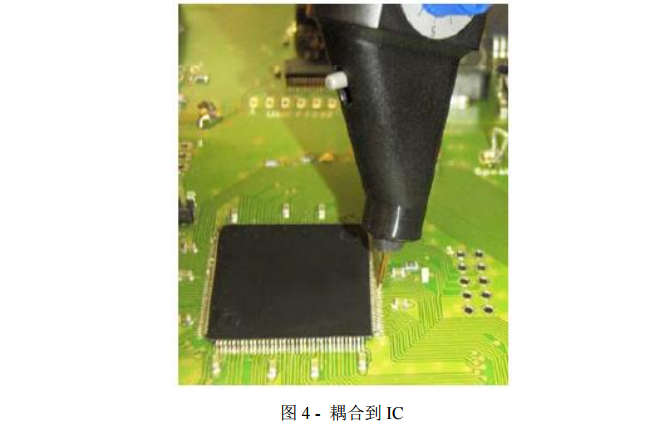

pF)耦合到被测设备中。可以调节极性和强度。例如,可更换的针电极被用于连接引脚。

这一原理有几个优点:1、要施加到该干扰具有结构之间的耦合电容和场源总是相同(不再取决于距离)。2、高度集成的电路封装(TQFP)的引脚可以单独地连接。3、与小结构相对的耦合电容增加。4、电路可以在应用程序进行测试。

由于在附近的一个真正的测试模块的信号,连接到脉冲发生器没有足够短接地是可行的,设计发生器以致使耦合到测试设备的电容是足够的。场源的脉冲形状最早在50Ω系统检查,用1GHz示波器,以确保由脉冲电压源产生的干扰足够大来干扰系统。

测量表明,产生的8 V脉冲是强到足以引起与IC的干扰,尽管电容电流返回路径(振幅和曲线形状取决于测量装置,例如,干扰被注入高阻抗的输入或驱动器输出)。干扰脉冲逐一施加到这种测量设置的每个IC引脚。最低脉冲频度最初选择在正极性。在第一次测试时,无功能故障可能被发现。之后逐渐增加频度,如与ESD静电枪合规测试同样的故障模式出现了。控制器可以作出由耦合到20线路中的2条线路引起的事故,这通向控制单元。只有两个修改最初认为是潜在的应对措施:对地阻塞电容器的安装和芯片电感的安装/在控制单元和控制器之间的线电阻。安装两个10 pF的0402电容后,P23又被应用到所有引脚。该故障并没有重新出现。

然后用ESD静电枪的合规测试重复。很明显,导致在两个测试的故障是相互关联的,抗扰能力提高到4.8kV。

五、 结论

设备抗扰度测试期间发生的干扰可以模拟,并且特别敏感的电路部件(IC引脚/线路)可以通过局部耦合成单独的线或IC的引脚进行标识。分析故障原因变得更容易,并且开发人员可以得到一个底部的故障要快得多。

参考文献

[1] "Neue Aspekte zur ESD-Störfestigkeit“ Elektronik, 05/2009, Author: Gunter Langer

[2] "Neue Burst-Generatoren zur Prüfung der Störfestigkeit von integrierten Schaltungen“,2004, Author: Gunter Langer, Bernd Deutschmann & Günther Auderer

@本文属于北京海洋兴业科技股份有限公司所有,如需转载,请注明出处。

- 上一篇:如何用磁场探头测定磁场强度和高频电流?

- 下一篇:提升电子模块抗脉冲干扰的能力