# PCI/PCIe/PXI-62204/62205/62206/62208

64-/96-CH High Performance Multi-Function Data Acquisition Card **User's Manual**

Manual Rev.

1.0.1

Revision Date:

Dec 07, 2021

Advance Technologies; Automate the World.

# Using this manual

# 1.1 Copyright

This document contains proprietary information protected by copyright. All rights are reserved. No part of this manual may be reproduced by any mechanical, electronic, or other means in any form without prior written permission of the manufacturer. All specifications are subject to change without further notice.

# 1.2 Audience and scope

This manual guides you when using JYTEK multi-function PCI/PCIe/PXI-62204/62205/62206/62208 card. The card'shardware, signal connections, and calibration information are provided for faster application building. This manual is intended for computer programmers and hardware engineers with advanced knowledge of data acquisition and high-level programming.

# 1.3 How this manual is organized

This manual is organized as follows:

**Chapter 1 Introduction**: This chapter intoduces the PCI/PCIe/PXI-62204/62205/62206/62208 card including its features, specifications and software support information.

**Chapter 2 Installation**: This chapter presents the card's layout, package contents, and installation.

**Chapter 3 Signal Connections**: This part describes the PCI/PCIe/PXI-62204/62205/62206/62208 card signal connections.

**Chapter 4 Operation Theory**: The operation theory of the PCI/PCIe/ PXI-62204/62205/62206/62208 card functions including A/D conversion, D/A conversion, and programmable function I/O are discussed in this chapter.

**Chapter 5 Calibration**: The chapter offers information on how to calibrate the PCI/PCIe/PXI-62204/62205/62206/62208 card for accurate data acquisition and output.

Warranty Policy: This presents the JYTEK Warranty Policy terms and coverages.

Getting Service: Contact information for JYTEK's worldwide offices.

## 1.4 Conventions

Take note of the following conventions used throughout the manual to make sure that you perform certain tasks and instructions properly.

| NOTE      | Additional information, aids, and tips that help you perform particular tasks.                                                          |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| IMPORTANT | Critical information and instructions that you MUST perform to complete a task.                                                         |

| WARNING   | Information that prevents physical injury, data loss, module damage, program corruption etc. when trying to complete a particular task. |

# **Table of Contents**

| Та  | Table of Contents i |                                         |       |  |

|-----|---------------------|-----------------------------------------|-------|--|

| Lis | t of Ta             | ıbles                                   | . iii |  |

| Lis | t of Fi             | gures                                   | . iv  |  |

| 1   | Intro               | duction                                 | . 1   |  |

|     | 1.1                 | Features                                | 2     |  |

|     | 1.2                 | Applications                            | 3     |  |

|     | 1.3                 | Specifications                          | 3     |  |

|     | 1.4                 | Software Support                        | 13    |  |

|     |                     | Programming Library                     | .13   |  |

| 2   | Insta               | lation                                  | 15    |  |

|     | 2.1                 | Contents of Package                     | 15    |  |

|     | 2.2                 | Unpacking                               | 15    |  |

|     | 2.3                 | Card Layout                             |       |  |

|     |                     | PCIe-62204/62205/62206/62208            | . 17  |  |

|     |                     | PCI-62204/62205/62206/62208             |       |  |

|     |                     | PXI-62204/62205/62206/62208             | . 18  |  |

|     | 2.4                 | PCI Configuration                       | 19    |  |

|     |                     | Plug and Play                           | . 19  |  |

|     |                     | Configuration                           | . 19  |  |

|     |                     | Troubleshooting                         | .19   |  |

| 3   | Signa               | I Connections                           | 21    |  |

|     | 3.1                 | Connectors Pin Assignment               | 21    |  |

|     |                     | CN1 Connector                           | .22   |  |

|     |                     | CN2 Connector                           | .24   |  |

|     |                     | SSI Connector                           | .28   |  |

|     | 3.2                 | Analog Input Signal Connection          | 29    |  |

|     |                     | Types of signal sources                 | .29   |  |

|     |                     | Input Configurations                    | .29   |  |

|     |                     | Differential Input Mode                 | .31   |  |

| 4   | Opera               | ation Theory                            | 33    |  |

|     | 4.1                 | A/D Conversion                          | 33    |  |

|     |                     | PCI/PCIe/PXI-62204/62208 AI Data Format | 33    |  |

| Ge | etting | Service                                                                            | 89       |

|----|--------|------------------------------------------------------------------------------------|----------|

| w  | arrant | y Policy                                                                           | 87       |

|    | 5.3    | Saving Calibration Constants                                                       | 86       |

|    | 5.2    | Auto-calibration                                                                   |          |

|    | 5.1    | Loading Calibration Constants                                                      |          |

| 5  |        | ration                                                                             |          |

| _  |        |                                                                                    | <b>.</b> |

|    |        | System Synchronization Interface                                                   |          |

|    |        | Auxiliary Function Inputs (AFI)                                                    |          |

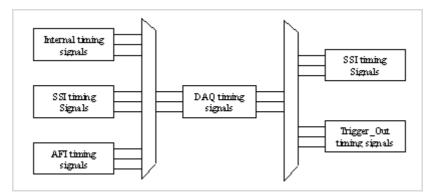

|    |        | DAQ timing signals                                                                 |          |

|    | 4.6    | User-controllable Timing Signals                                                   |          |

|    |        | External Analog Trigger                                                            | 70       |

|    |        | Software-Trigger                                                                   | 70       |

|    | 4.5    | Trigger Sources                                                                    |          |

|    |        | General Purpose Timer/Counter modes                                                |          |

|    |        | The Basics of Timer/Counter Functions                                              |          |

|    | 4.4    | General Purpose Timer/Counter Operation                                            |          |

|    | 4.3    | Digital I/O                                                                        |          |

|    |        | Trigger Modes                                                                      |          |

|    |        | Timed Waveform Generation                                                          |          |

|    |        | Software Update                                                                    |          |

|    | 4.2    | D/A Conversion                                                                     |          |

|    |        | Bus-mastering DMA Data Transfer                                                    |          |

|    |        | Trigger Modes                                                                      | -        |

|    |        | nel Gain Queue                                                                     |          |

|    |        | Specifying Channels, Gains, and Input Configurations in the C                      |          |

|    |        | Programmable Scan Acquisition Mode                                                 |          |

|    |        | Software Conversion with Polling Data Transfer Acquisition M<br>(Software Polling) |          |

|    |        | PCI/PCIe/PXI-62205/62206 AI Data Format                                            |          |

|    |        | DCI/DCIa/DVI 6220E/62206 AL Data Format                                            | 26       |

# **List of Tables**

| Table :<br>Table : |       | Programmabel Input Range<br>Bandwidth                       |     |

|--------------------|-------|-------------------------------------------------------------|-----|

| Table              |       |                                                             |     |

|                    | -     | System Noise                                                |     |

| Table              |       | CMRR (DC to 60 Hz)                                          |     |

| Table              | -     | Settling Time to Full Scale Step                            | /   |

| Table              | 3-1:  | CN1 Pin Assignment for PCI/PCIe/PXI-62204/62205/62206 22    |     |

| Table              | 3-2:  | CN1 Pin Assignment for PCI/PCIe/PXI-62208 23                | 3   |

| Table              | 3-3:  | CN2 Pin Assignment for PCI/PCIe/PXI-62204/62205/62206<br>24 |     |

| Table              | 3-4:  | CN2 Pin Assignment for PCI/PCIe/PXI-62208 25                | 5   |

| Table              | 3-5:  | CN1/CN2 Signal Description                                  | 5   |

| Table              | 3-6:  | SSI Connector Pin Assignment 28                             | 3   |

| Table              | 3-7:  | SSI Connector Legend                                        | 3   |

| Table              | 4-1:  | Bipolar Analog Input Range and Output Digital Code on PCI   | 1/  |

|                    |       | PCIe/PXI-62204/62208                                        | 5   |

| Table              | 4-2:  | Unipolar Analog Input Range and Output Digital Code on Pe   | CI/ |

|                    |       | PCIe/PXI-62204/62208                                        | 5   |

| Table              | 4-3:  | Bipolar Analog Input Range and Output Digital Code for PC   | 1/  |

|                    |       | PCIe/PXI-62205/62206                                        | 5   |

| Table              | 4-4:  | Unipolar Analog Input Range and Output Digital Code for P   | CI/ |

|                    |       | PCIe/PXI-62205/62206                                        | 5   |

| Table              | 4-5:  | Bipolar Output Code Table 53                                | 3   |

| Table              | 4-6:  | Unipolar Output Code Table 54                               | 4   |

| Table              | 4-7:  | Analog Trigger SRC1 (EXTATRIG) Ideal Transfer Characterist  | tic |

| Table              | 4-8:  | User-controllable Timing Signals and Functionalities 77     | 7   |

| Table              | 4-9:  | Auxiliary Function Input Signals and Functionalities 79     | Э   |

| Table              | 4-10: | SSI Timing Signal and Functions 81                          | 1   |

# **List of Figures**

| Figure 2-1:  | PCIe-62204/62205/62206/62208 Card Layout                  | 17    |

|--------------|-----------------------------------------------------------|-------|

| Figure 2-2:  | PCI-62204/62205/62206/62208 Card Layout                   | 18    |

| Figure 2-3:  | PXI-62204/62205/62206/62208 Card Layout                   | 18    |

| Figure 3-1:  | Floating Source and RSE Input Connections                 | 30    |

| Figure 3-2:  | Ground-referenced Sources and NRSE Input Connections      | s 30  |

| Figure 3-3:  | Ground-referenced Source and Differential Input           | 31    |

| Figure 3-4:  | Floating Source and Differential Input                    | 31    |

| Figure 4-1:  | Synchronous Digital Inputs Block Diagram                  | 34    |

| Figure 4-2:  | Synchronous Digital Inputs Timing                         | 34    |

| Figure 4-3:  | Scan Timing                                               | 39    |

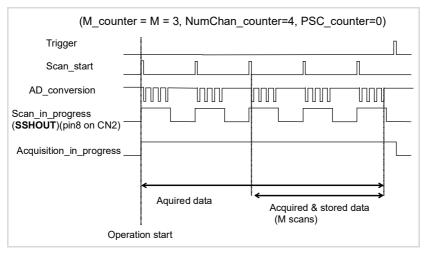

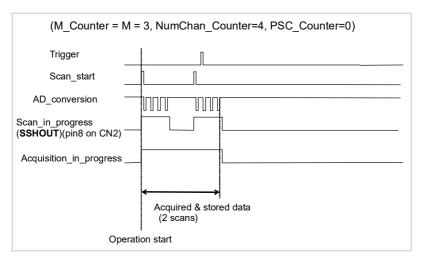

| Figure 4-4:  | Pre-trigger (Trigger occurs after M scans)                | 42    |

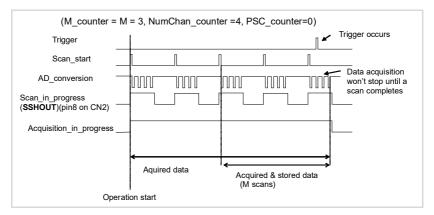

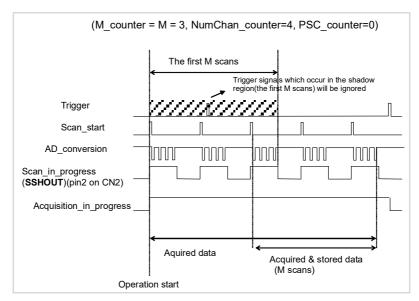

| Figure 4-5:  | Pre-trigger (Trigger with scan in progress)               | 43    |

| Figure 4-6:  | Pre-trigger with M_enable=0 (Trigger occurs before M so   | cans) |

|              | 44                                                        |       |

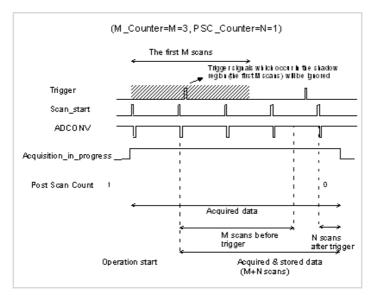

| Figure 4-7:  | Pre-trigger with M_enable=1                               |       |

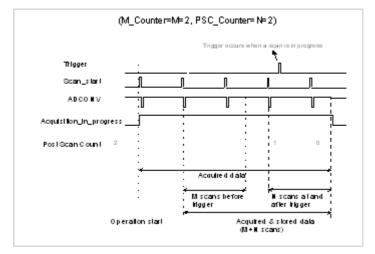

| Figure 4-8:  | Middle-Trigger with M_enable = 1                          | 46    |

| Figure 4-9:  | Middle-Trigger (Trigger occurs when a scan is in progress | s) 47 |

| Figure 4-10: | Post-trigger                                              | 48    |

| Figure 4-11: | Delay trigger                                             | 49    |

| Figure 4-12: | Post trigger with Re-trigger                              | 50    |

| Figure 4-13: | Scatter/gather DMA for Data Transfer                      | 52    |

| Figure 4-14: | Typical D/A Timing of Waveform Generation                 | 56    |

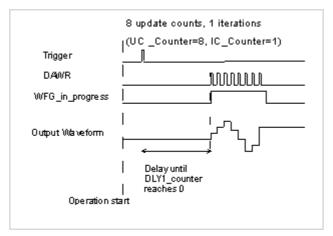

| Figure 4-15: | Post Trigger Waveform Generation                          | 57    |

| Figure 4-16: | Delay Trigger Waveform Generation                         | 58    |

| Figure 4-17: | Re-triggered Waveform Generation with Post-Trigger        |       |

|              | (DLY2_Counter=0)                                          | 58    |

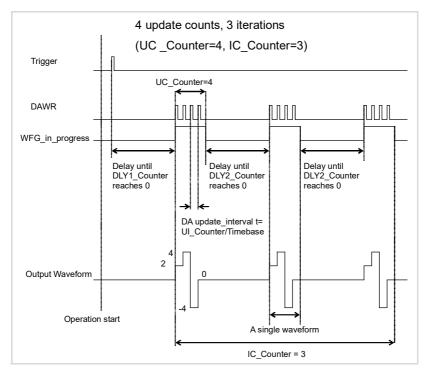

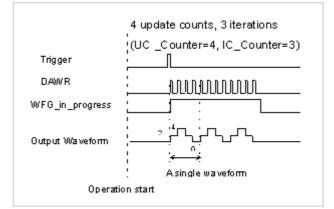

| Figure 4-18: | Finite Iterative Waveform Generation with Post-trigger    |       |

|              | (DLY2_Counter = 0)                                        |       |

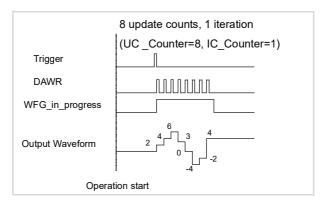

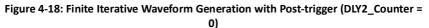

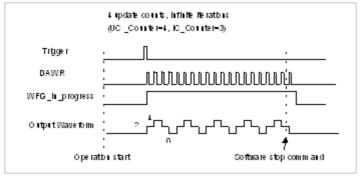

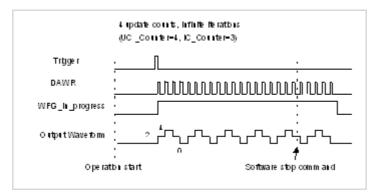

| Figure 4-19: | Infinite Iterative Waveform Generation with Post-trigger  | -     |

|              | (DLY2_Counter = 0)                                        | 60    |

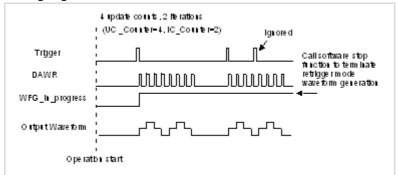

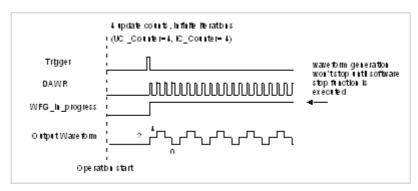

| Figure 4-20: | Stop Mode I                                               | 61    |

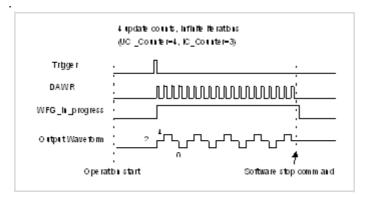

| Figure 4-21: | Stop Mode II                                              | 62    |

| Figure 4-22: | Stop Mode III                                             | 62    |

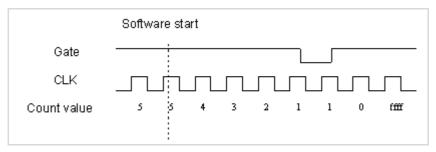

| Figure 4-23: | Mode1 Operation                                           | 65    |

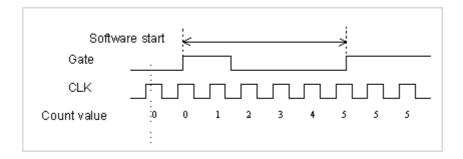

| Figure 4-24: | Mode2 Operation                                           |       |

| Figure 4-25: | Mode3 Operation                                           |       |

| Figure 4-26: | Mode4 Operation                                           |       |

| Figure 4-27: | Mode5 Operation                                           | 68    |

| Figure 4-28: | Mode6 Operation                          | 68 |

|--------------|------------------------------------------|----|

| Figure 4-29: | Mode7 Operation                          | 69 |

| Figure 4-30: | Mode8 Operation                          | 69 |

| Figure 4-31: | Analog Trigger Block Diagram             | 71 |

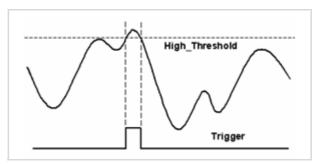

| Figure 4-32: | Below-Low Analog Trigger Condition       | 72 |

| Figure 4-33: | Above-High Analog Trigger Condition      | 72 |

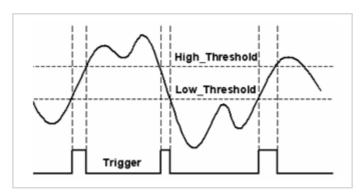

| Figure 4-34: | Inside-Region Analog Trigger Condition   | 73 |

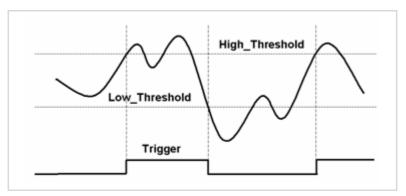

| Figure 4-35: | High-Hysteresis Analog Trigger Condition | 74 |

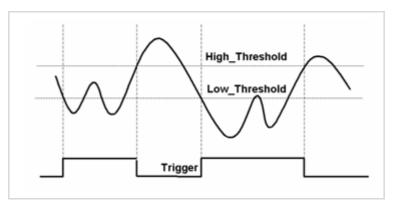

| Figure 4-36: | Low-Hysteresis Analog Trigger Condition  | 74 |

| Figure 4-37: | External Digital Trigger                 | 75 |

| Figure 4-38: | DAQ signals routing                      | 76 |

# 1 Introduction

The PCI/PCIe/PXI-62204/62205/62206/62208 card is an advanced data acquisition card based on the 32-bit PCI or PCI Express<sup>®</sup> architecture. High performance designs and state-of-the-art technology make these cards ideal for data logging and signal analysis applications in medical, process control, etc.

## 1.1 Features

The PCI/PCIe/PXI-62204/62205/62206/62208 advanced data acquisition card has the following features:

- 32-bit PCI bus (PCI/PXI models) or PCI Express (PCIe model), plug and play

- ► Up to 96 single-ended inputs or 48 differential inputs supporting combinations of SE and DI analog input signals

- Up to 1024 words analog input Channel Gain Queue configuration size

- Analog input resolution and sampling rate:

- ▷ PCI/PCIe/PXI-62204/62208: 12-bit and up to 3 MHz

- ▷ PCI/PCIe/PXI-62205: 16-bit and up to 500 KHz

- ▷ PCI/PCIe/PXI-62206: 16-bit and up to 250 KHz

- Programmable bipolar/unipolar analog input

- ▶ Programmable gain:

- PCI/PCIe/PXI-62204/62208: x1, x2, x4, x5, x8, x10, x20, x40, x50, x200

- ▷ PCI/PCIe/PXI-62205/62206: x1, x2, x4, x8

- ► A/D FIFO size: 1024 samples

- Versatile trigger sources: software trigger, external digital trigger, analog trigger and trigger from System Synchronization Interface (SSI)

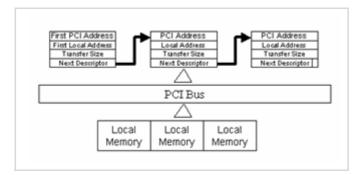

- A/D data transfer: software polling and bus-mastering DMA with scatter/gather functionality

- ► Four A/D trigger modes including post-trigger, delay-trigger, pretrigger and middle-trigger

- Two-channel D/A outputs with waveform generation capability (except PCI/PCIe/PXI-62208)

- ▶ 1024 word length output data FIFO for D/A channels

- D/A data transfer: Software update and bus-mastering DMA with scatter/gather functionality

- Support System Synchronization Interface (SSI)

- ▶ Full A/D and D/A auto-calibration

- Jumper-free and software-configurable

## 1.2 Applications

- Automotive Testing

- Cable Testing

- ▶ Transient signal measurement

- ► ATE

- Laboratory Automation

- Biotech measurement

# 1.3 Specifications

### Analog Input (AI)

- ▶ Programmable channels:

- PCI/PCIe/PXI-62204/62205/62206: 64 single-ended (SE) or 32 differential input (DI)

- PCI/PCIe/PXI-62208: 96 single-ended (SE) or 48 differential input (DI)

- Mixing of SE and DI analog signal sources (Software selectable per channel)

- ► A/D converter:

- ▷ PCI/PCIe/PXI-62204/62208: LT1412 or equivalent

- ▷ PCI/PCIe/PXI-62205: A/D7665 or equivalent

- ▷ PCI/PCIe/PXI-62206: A/D7663 or equivalent

- Max sampling rate:

- PCI/PCIe/PXI-62204/62208: 3 MS/s (single-channel) 1 MS (s (multi shanne)

1 MS/s (multi-channel)

- ▷ PCI/PCIe/PXI-62205: 500 kS/s

- ▷ PCI/PCIe/PXI-62206: 250 kS/s

- Resolution:

- ▷ PCI/PCIe/PXI-62204/62208: 12-bit, no missing code

- ▷ PCI/PCIe/PXI-62205/62206: 16-bit, no missing code

- Input coupling: DC

- ► FIFO buffer size:

- ▷ PCI/PCIe/PXI-62204: 8K samples

- ▷ PCI/PCIe/PXI-62205/62206/62208: 512 samples

Programmable input range:

| Device Bipolar input range |         | Unipolar input range |  |

|----------------------------|---------|----------------------|--|

|                            | ±10 V   | —                    |  |

|                            | ±5 V    | 0 to 10 V            |  |

|                            | ±2.5 V  | 0 to 5 V             |  |

|                            | ±2 V    | 0 to 4 V             |  |

| 62204/                     | ±1.25 V | 0 to 2.5 V           |  |

| 62208                      | ±1 V    | 0 to 2 V             |  |

|                            | ±0.5 V  | 0 to 1 V             |  |

|                            | ±0.25 V | 0 to 0.5 V           |  |

|                            | ±0.2 V  | 0 to 0.4 V           |  |

|                            | ±0.05 V | 0 to 0.1 V           |  |

|                            | ±10 V   | 0 to 10 V            |  |

| 62205/                     | ±5 V    | 0 to 5 V             |  |

| 62206                      | ±2.5 V  | 0 to 2.5 V           |  |

|                            | ±1.25 V | 0 to 1.25 V          |  |

- ▶ Operational common mode voltage range: ±11V

- ► Over-voltage protection:

- ▷ Power on: Continuous ±30V

- ▷ Power off: Continuous ±15V

- ► FIFO buffer size: 1024 samples

- ► Data transfers:

- ▷ Programmed I/O

- ▷ Bus-mastering DMA with scatter/gather

- ► Channel Gain Queue configuration size:

- ▷ PCI/PCIe/PXI-62204/62205/62206: 512 words

- ▷ PCI/PCIe/PXI-62208: 1024 words

| ► | Bandwidth (Typical 25°C): |

|---|---------------------------|

|---|---------------------------|

| Device | Inp     | ut range      | Small signal<br>bandwidth<br>(-3dB) | Large signal<br>bandwidth<br>(1% THD) |

|--------|---------|---------------|-------------------------------------|---------------------------------------|

|        | ±10 V   | _             |                                     |                                       |

|        | ±5 V    | 0 V to 10 V   | 2000 kHz                            |                                       |

|        | ±2.5 V  | 0 V to 5 V    | 2000 KH2                            | —                                     |

|        | ±1.25 V | 0 V to 2.5 V  |                                     |                                       |

| 62204/ | ±2 V    | 0 V to 4 V    | 1450 kHz                            |                                       |

| 62208  | ±0.5 V  | 0 V to 1 V    | 1450 KHZ                            | —                                     |

|        | ±1 V    | 0 V to 2 V    | 990 kHz                             | —                                     |

|        | ±0.25 V | 0 V to 0.5 V  | 990 KHZ                             |                                       |

|        | ±0.2 V  | 0 V to 0.4 V  | 240 kHz                             |                                       |

|        | ±0.05 V | 0 V to 0.1 V  | 240 KHZ                             | —                                     |

|        | ±10 V   | 0 V to 0 V    | 1600 kHz                            | 300 kHz                               |

| 62205  | ±5 V    | 0 V to 5 V    | 1400 kHz                            | 310 kHz                               |

| 02205  | ±2.5 V  | 0 V to 2.5 V  | 1000 kHz                            | 310 kHz                               |

|        | ±1.25 V | 0 V to 1.25 V | 600 kHz                             | 330 kHz                               |

|        | ±10 V   | 0 V to 10 V   | 760 kHz                             | 300 kHz                               |

| 62206  | ±5 V    | 0 V to 5 V    | 720 kHz                             | 310 kHz                               |

| 62206  | ±2.5 V  | 0 V to 2.5 V  | 610 kHz                             | 310 kHz                               |

|        | ±1.25 V | 0 V to 1.25 V | 450 kHz                             | 330 kHz                               |

Table 1-2: Bandwidth

| Device | Input Range | System Noise | Input Range   | System Noise |

|--------|-------------|--------------|---------------|--------------|

|        | ±10 V       | 0.95 LSBrms  | 0 V to 10 V   | 1.5 LSBrms   |

| 62205  | ±5 V        | 1.0 LSBrms   | 0 V to 5 V    | 1.6 LSBrms   |

| 62205  | ±2.5 V      | 1.1 LSBrms   | 0 V to 2.5 V  | 1.7 LSBrms   |

|        | ±1.25 V     | 1.3 LSBrms   | 0 V to 1.25 V | 1.9 LSBrms   |

| 62206  | ±10 V       | 0.8 LSBrms   | 0 V to 10 V   | 0.9 LSBrms   |

|        | ±5 V        | 0.85 LSBrms  | 0 V to 5 V    | 1.0 LSBrms   |

|        | ±2.5 V      | 0.85 LSBrms  | 0 V to 2.5 V  | 1.0 LSBrms   |

|        | ±1.25 V     | 0.9 LSBrms   | 0 V to 1.25 V | 1.2 LSBrms   |

► System Noise (LSBrms, including Quantization, Typical, 25°C)

Table 1-3: System Noise

- ► Input impedance:

- $\triangleright$  Normal power on: 1 G $\Omega$ /100 pF

- $\triangleright$  Power off: 820  $\Omega$

- $\triangleright$  Overload: 820  $\Omega$

- ► CMRR (DC to 60 Hz, Typical)

| Device          | Input Range | CMRR  | Input Range   | CMRR  |

|-----------------|-------------|-------|---------------|-------|

| 62204/<br>62208 | All ranges  | 90 dB | —             | _     |

|                 | ±10 V       | 83 dB | 0 V to 10 V   | 87 dB |

| 62205/          | ±5 V        | 87 dB | 0 V to 5 V    | 90 dB |

| 62206           | ±2.5 V      | 90 dB | 0 V to 2.5 V  | 92 dB |

|                 | ±1.25 V     | 92 dB | 0 V to 1.25 V | 93 dB |

Table 1-4: CMRR (DC to 60 Hz)

| ► | Settling time to full-scale step (Typical, 25°C): |  |

|---|---------------------------------------------------|--|

|---|---------------------------------------------------|--|

| Device | Input Range              |            | Condition                                                                                                       | Settling time                              |  |

|--------|--------------------------|------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------|--|

|        | ±10 V                    |            | Multiple channels,                                                                                              |                                            |  |

|        | ±5 V                     | 0 to 10 V  | multiple ranges.                                                                                                |                                            |  |

|        | ±2.5 V                   | 0 to 5 V   | <ul> <li>All samples in unipolar/<br/>bipolar mode.</li> </ul>                                                  | 1 us to 0 1% arror                         |  |

|        | ±2 V                     | 0 to 4 V   | Sipolar mode.                                                                                                   | 1 μs to 0.1% error                         |  |

|        | ±1.25 V                  | 0 to 2.5 V |                                                                                                                 |                                            |  |

|        | ±0.5 V                   | 0 to 1 V   |                                                                                                                 |                                            |  |

|        | ±1                       | 0 V        | Multiple channels,                                                                                              |                                            |  |

|        | ±5 V                     | 0 to 10 V  | multiple ranges.                                                                                                |                                            |  |

| 62204/ | ±2.5 V                   | 0 to 5 V   | <ul> <li>All samples in unipolar/<br/>bipolar mode.</li> </ul>                                                  | 1.25                                       |  |

| 62204/ | v2 V                     | 0 to 4 V   | Sipolar mode.                                                                                                   | 1.25 μs to 0.1% error                      |  |

|        | ±1.25 V                  | 0 to 2.5 V |                                                                                                                 |                                            |  |

|        | ±0.5 V                   | 0 to 1 V   |                                                                                                                 |                                            |  |

|        | ±1 V                     | 0 to 2 V   | <ul> <li>Multiple channels,<br/>multiple ranges.</li> </ul>                                                     |                                            |  |

|        | ±0.25 V                  | 0 to 0.5 V | • All samples in unipolar/<br>bipolar mode.                                                                     | 2 μs to 0.1% error                         |  |

|        | ±0.2 V                   | 0 to 0.4 V | <ul> <li>Multiple channels,<br/>multiple ranges.</li> </ul>                                                     | 5 0.40/                                    |  |

|        | ±0.05 V                  | 0 to 0.1 V | • All samples in unipolar/<br>bipolar mode.                                                                     | 5 μs to 0.1% error                         |  |

| 62205/ | All Ranges<br>All Ranges |            | <ul> <li>Multiple channels,<br/>multiple ranges.</li> <li>All samples in unipolar/<br/>bipolar mode.</li> </ul> | 2 μs to 0.1% error,<br>4 μs to 0.01% error |  |

| 62206  |                          |            | <ul> <li>Multiple channels,<br/>multiple ranges.</li> <li>All samples in unipolar/<br/>bipolar mode.</li> </ul> | 2 μs to 0.2% error,<br>4 μs to 0.01% error |  |

Table 1-5: Settling Time to Full Scale Step

- Time-base source:

- Internal 40 MHz or external clock Input (f<sub>max</sub>: 40 MHz, f<sub>min</sub>: 1 MHz, 50% duty cycle)

- Trigger modes: Post-trigger, delay-trigger, pre-trigger and middletrigger

- Offset error:

- ▷ Before calibration: ±60 mV max

- ▷ After calibration: ±1 mV max

- Gain error (relative to calibration reference):

- ▷ Before calibration: 0.6% of reading

- $\triangleright$  After calibration (gain = 1):

0.03% of reading max for PCI/PCIe/PXI-62204/62208

0.01% of reading max for PCI/PCIe/PXI-62205/62206

▷ Gain 1 with gain error adjusted to 0 at gain=1:

0.05% of reading max

## Analog Output (AO)

| NOTE                                                       | The PCI/PCIe/PXI-62208 card does not support this function                    |  |  |  |  |

|------------------------------------------------------------|-------------------------------------------------------------------------------|--|--|--|--|

| ►                                                          | Channels: Two-channel analog voltage output                                   |  |  |  |  |

| ►                                                          | DA converter: LTC7545 or equivalent                                           |  |  |  |  |

| ►                                                          | Max update rate: 1 MS/s                                                       |  |  |  |  |

| ►                                                          | Resolution: 12-bit                                                            |  |  |  |  |

| ►                                                          | FIFO buffer size:                                                             |  |  |  |  |

|                                                            | 512 samples per channel when both channels are enabled for<br>timed DA output |  |  |  |  |

|                                                            | 1024 samples when only one channel is used for timed DA output                |  |  |  |  |

| ►                                                          | Data transfers:                                                               |  |  |  |  |

|                                                            | Programmed I/O                                                                |  |  |  |  |

|                                                            | Bus-mastering DMA with scatter/gather                                         |  |  |  |  |

| ►                                                          | Output range: ±10 V, 0 V to 10 V, ±AOEXTREF, 0 to AOEXTREF                    |  |  |  |  |

| <ul> <li>Settling time: 3 S to 0.5 LSB accuracy</li> </ul> |                                                                               |  |  |  |  |

| ► Slew rate: 20 V/µS                                       |                                                                               |  |  |  |  |

| <ul> <li>Output coupling: DC</li> </ul>                    |                                                                               |  |  |  |  |

| ►                                                          | <ul> <li>Protection: Short-circuit to ground</li> </ul>                       |  |  |  |  |

| ►                                                          | Output impedance: 0.01 $\Omega$ typical                                       |  |  |  |  |

| ►                                                          | Output driving current: ±5 mA max                                             |  |  |  |  |

| ►                                                          | Stability: Any passive load, up to 1500 pF                                    |  |  |  |  |

| ►                                                          | Power-on state: 0V steady-state                                               |  |  |  |  |

| ►                                                          | Power-on glitch: ±1.5 V/500 μS                                                |  |  |  |  |

| ►                                                          | Relative accuracy: ±0.5 LSB typical, ±1 LSB max                               |  |  |  |  |

| ►                                                          | DNL: ±0.5 LSB typical, ±1.2 LSB max                                           |  |  |  |  |

| ►                                                          | Offset error:                                                                 |  |  |  |  |

|                                                            | Before calibration: ±80 mV max                                                |  |  |  |  |

|                                                            | After calibration: ±1 mV max                                                  |  |  |  |  |

| ►                                                          | Gain error:                                                                   |  |  |  |  |

|                                                            | Before calibration: ±0.8% of output max                                       |  |  |  |  |

|                                                            | •                                                                             |  |  |  |  |

## General Purpose Digital I/O (G.P. DIO, 82C55A)

- Channels: 24 programmable input/output

- Compatibility: TTL

- Input voltage:

- ▷ Logic Low: VIL=0.8 V max; IIL=0.2 mA max

- ▷ High: VIH=2.0 V max; IIH=0.02 mA max

- Output voltage:

- ▷ Low: VOL=0.5 V max; IOL=8 mA max

- $\triangleright$  High: VOH=2.7 V min; IOH=400  $\mu$ A

- Synchronous Digital Inputs (SDI): On PCI/PCIe/PXI-62204 model only.

- Channels: 8 digital inputs sampled simultaneously with the analog signal input

- ▷ Compatibility: TTL/CMOS

- ▷ Input voltage:

Logic Low: VIL=0.8 V max; IIL=0.2mA max

Logic High: VIH=2.7 V min; IIL=0.02mA max

#### **General Purpose Timer/Counter (GPTC)**

#### **NOTE** The PCI/PCIe/PXI-62208 does not support this function.

- Channels: 2 independent up/down timer/counters

- Resolution: 16-bit

- ► Compatibility: TTL

- Clock source: Internal or external

- ▶ Max source frequency: 10 MHz

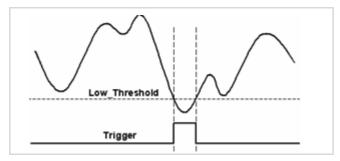

### Analog Trigger (A.Trig)

- ► Source:

- ▷ All analog input channels

- ▷ External analog trigger (EXTATRIG)

- ▶ Level: ±Full-scale, internal; ±10 V external

- Resolution: 8-bit

- Slope: Positive or negative (software-selectable)

- ► Hysteresis: Programmable

- ▶ Bandwidth: 400 kHz

#### External Analog Trigger Input (EXTATRIG)

- ► Input Impedance:

- $\triangleright$  40 k $\Omega$  for PCI/PCIe/PXI-62204/62208

- $\,\triangleright\,\,$  20 k $\Omega$  for PCI/PCIe/PXI-62205/62206

- ► Coupling: DC

- ▶ Protection: Continuous ±35 V maximum

#### Digital Trigger (D.Trig)

- Compatibility: TTL/CMOS

- ► Response: Rising or falling edge

- ▶ Pulse Width: 10 ns min

#### System Synchronous Interface (SSI)

► Trigger lines: 7

#### Stability

- ▶ Recommended warm-up time: 15 minutes

- On-board calibration reference:

- ▷ Level: 5.000 V

- ▷ Temperature coefficient: ±2 ppm/°C

- ▷ Long-term stability: 6 ppm/1000 Hr

### Physical

- ► Dimensions:

- 175mm by 107mm for PCI/PCIe62204/62205/62206/62208

- Standard CompactPCI form factor for PXI-62204/62205/62206/ 62208

- ▶ I/O connector: 68-pin female VHDCI type (e.g. AMP-787254-1)

## Power Requirement (typical)

- ► +5 VDC

- ▷ 1.3 A for PCI/PCIe/PXI-62204

- ▷ 1.2 A for PCI/PCIe/PXI-62205/62206

- ▷ 950 mA for PCI/PCIe/PXI-62208

- ► +12 VDC

- $\triangleright$  358 mA for PCIe-62204

- 344 mA for PCIe-62205

- ▷ 390 mA for PCIe-62206

- > 258 mA for PCIe-62208

- ► +3.3 VDC

- 815 mA for PCIe-62204

- > 735 mA for PCIe-62205

- 710 mA for PCIe-62206

- 815 mA for PCIe-62208

### **Operating Environment**

- ► Ambient temperature: 0°C to 55°C

- ▶ Relative humidity: 10% to 90% non-condensing

#### Storage Environment

- ► Ambient temperature: -20°C to 80°C

- ▶ Relative humidity: 5% to 95% non-condensing

## 1.4 Software Support

JYTEK provides versatile software drivers and packages for users' different approach to building up a system. JYTEK not only provides programming libraries such as DLL for most Windows-based systems, but also provide drivers for other software packages.

Contact your JYTEK to get the free SeeSharp open source software.

### **Programming Library**

For customers who are writing their own programs, we provide function libraries for many different operating systems, including:

D2K-DASK: Include device drivers and DLL for Windows<sup>®</sup> 7/10. DLL is binary compatible across Windows 7/10. This means all applications developed with D2K-DASK are compatible across Windows 7/10. The developing environment can be VB, VC++, Delphi, BC5, or any Windows programming language that allows calls to a DLL. The user's guide and function reference manual of D2K-DASK are on the website. (www.jytek.com)

D2K-DASK/X: Include device drivers and shared library for Linux. The developing environment can be Gnu C/C++ or any programming language that allows linking to a shared library. The user's guide and function reference manual of D2K-DASK/X are on the website. (www.jytek.com)

# 2 Installation

This chapter describes how to install the PCI/PCIe/PXI-62204/62205/ 62206/62208 card. The contents of the package and unpacking information that you should be aware of are outlined first.

The PCI/PCIe/PXI-62204/62205/62206/62208 card performs an automatic configuration of the IRQ and port address. You can use the PCI\_SCAN software utility to read the system configuration.

## 2.1 Contents of Package

In addition to this User's Manual, the package includes the following items:

PCI/PCIe/PXI-62204/62205/62206/62208 multi-function data acquisition card

If any of these items are missing or damaged, contact the dealer from whom you purchased the product. Save the shipping materials and carton in case you want to ship or store the product in the future.

# 2.2 Unpacking

YourPCI/PCIe/PXI-62204/62205/62206/62208cardcontainselectro-static sensitive components that can be easily be damaged by static electricity.

Therefore, the card should be handled on a grounded anti-static mat. The operator should be wearing an anti-static wristband, grounded at the same point as the anti-static mat.

Inspect the card package for obvious damages. Shipping and handling may cause damage to the card. Be sure there are no shipping and handling damages on the modules carton before continuing.

After opening the card module carton, extract the system module and place it only on a grounded anti-static surface with component side up.

Again, inspect the module for damages. Press down on all the socketed IC's to make sure that they are properly seated. Do this only with the module place on a firm flat surface.

You are now ready to install your PCI/PCIe/PXI-62204/62205/62206/ 62208 card.

## 2.3 Card Layout

## PCIe-62204/62205/62206/62208

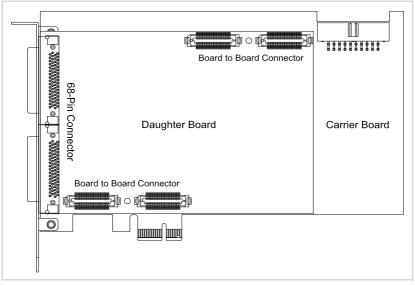

Figure 2-1: PCIe-62204/62205/62206/62208 Card Layout

## PCI-62204/62205/62206/62208

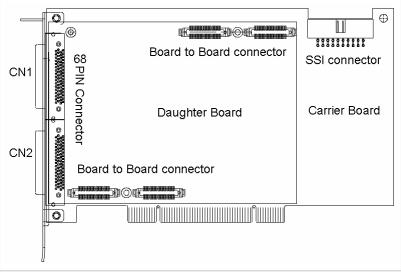

Figure 2-2: PCI-62204/62205/62206/62208 Card Layout

## PXI-62204/62205/62206/62208

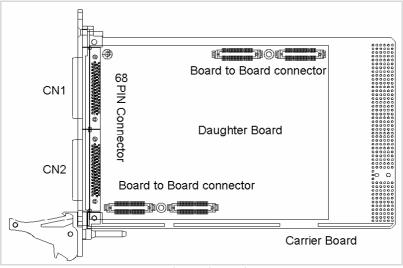

Figure 2-3: PXI-62204/62205/62206/62208 Card Layout

## 2.4 PCI Configuration

### **Plug and Play**

With support for plug and play, the card requests an interrupt number via its PCI controller. The system BIOS responds with an interrupt assignment based on the card information and on known system parameters. These system parameters are determined by the installed drivers and the hardware load seen by the system.

## Configuration

The board configuration is done on a board-by-board basis for all PCI boards in the system. Because configuration is controlled by the system and software, there is no jumper setting required for base address, DMA, and interrupt IRQ.

The configuration is subject to change with every boot of the sys-tem as new boards are added or removed.

### Troubleshooting

If your system doesn't boot or if you experience erratic operation with your PCI board in place, it is likely caused by an interrupt con-flict. The BIOS Setup may be incorrectly configured. Consult the BIOS documentation that comes with your system to solve this problem.

# **3** Signal Connections

This chapter describes PCI/PCIe/PXI-62204/62205/62206/62208 card connectors and the signal connection between the PCI/PCIe/PXI-62204/ 62205/62206/62208 card and external devices.

## 3.1 Connectors Pin Assignment

The PCI/PCIe/PXI-62204/62205/62206/62208 card is equipped with two 68-pin VHDCI-type connector (AMP-787254-1). It is used for digital input/output, analog input/output, timer/counter signals, etc. One 20-pin ribbon male connector is used for SSI (System Synchronous Interface) in PCI/PCIe-62204/62205/62206/62208 card. The pin assignments of the connectors are defined in Table 3-1, Table 3-2, Table 3-3, and Table 3-4.

## **CN1** Connector

|              |    |    | l .          |

|--------------|----|----|--------------|

| AIO (AIHO)   | 1  | 35 | (AILO) AI32  |

| AI1 (AIH1)   | 2  | 36 | (AIL1) AI33  |

| AI2 (AIH2)   | 3  | 37 | (AIL2) AI34  |

| AI3 (AIH3)   | 4  | 38 | (AIL3) AI35  |

| AI4 (AIH4)   | 5  | 39 | (AIL4) AI36  |

| AI5 (AIH5)   | 6  | 40 | (AIL5) AI37  |

| AI6 (AIH6)   | 7  | 41 | (AIL6) AI38  |

| AI7 (AIH7)   | 8  | 42 | (AIL7) AI39  |

| AI8 (AIH8)   | 9  | 43 | (AIL8) AI40  |

| AI9 (AIH9)   | 10 | 44 | (AIL9) AI41  |

| AI10 (AIH10) | 11 | 45 | (AIL10) AI42 |

| AI11 (AIH11) | 12 | 46 | (AIL11) AI43 |

| AI12 (AIH12) | 13 | 47 | (AIL12) AI44 |

| AI13 (AIH13) | 14 | 48 | (AIL13) AI45 |

| AI14 (AIH14) | 15 | 49 | (AIL14) AI46 |

| AI15 (AIH15) | 16 | 50 | (AIL15) AI47 |

| AISENSE      | 17 | 51 | AIGND        |

| AI16 (AIH16) | 18 | 52 | (AIL16) AI48 |

| AI17 (AIH17) | 19 | 53 | (AIL17) AI49 |

| AI18 (AIH18) | 20 | 54 | (AIL18) AI50 |

| AI19 (AIH19) | 21 | 55 | (AIL19) AI51 |

| AI20 (AIH20) | 22 | 56 | (AIL20) AI52 |

| AI21 (AIH21) | 23 | 57 | (AIL21) AI53 |

| AI22 (AIH22) | 24 | 58 | (AIL22) AI54 |

| AI23 (AIH23) | 25 | 59 | (AIL23) AI55 |

| AI24 (AIH24) | 26 | 60 | (AIL24) AI56 |

| AI25 (AIH25) | 27 | 61 | (AIL25) AI57 |

| AI26 (AIH26) | 28 | 62 | (AIL26) AI58 |

| AI27 (AIH27) | 29 | 63 | (AIL27) AI59 |

| AI28 (AIH28) | 30 | 64 | (AIL28) AI60 |

| AI29 (AIH29) | 31 | 65 | (AIL29) AI61 |

| AI30 (AIH30) | 32 | 66 | (AIL30) AI62 |

| AI31 (AIH31) | 33 | 67 | (AIL31) AI63 |

| EXTATRIG     | 34 | 68 | AIGND        |

|              |    |    |              |

Table 3-1: CN1 Pin Assignment for PCI/PCIe/PXI-62204/62205/62206

\* Symbols in "()" are for differential mode connection.

| AIO (AIHO)   | 1  | 35 | (AILO) AI48  |

|--------------|----|----|--------------|

| AI1 (AIH1)   | 2  | 36 | (AIL1) AI49  |

| AI2 (AIH2)   | 3  | 37 | (AIL2) AI50  |

| AI3 (AIH3)   | 4  | 38 | (AIL3) AI51  |

| AI4 (AIH4)   | 5  | 39 | (AIL4) AI52  |

| AI5 (AIH5)   | 6  | 40 | (AIL5) AI53  |

| AI6 (AIH6)   | 7  | 41 | (AIL6) AI54  |

| AI7 (AIH7)   | 8  | 42 | (AIL7) AI55  |

| AISENSE      | 9  | 43 | AIGND        |

| AI8 (AIH8)   | 10 | 44 | (AIL8) AI56  |

| AI9 (AIH9)   | 11 | 45 | (AIL9) AI57  |

| AI10 (AIH10) | 12 | 46 | (AIL10) AI58 |

| AI11 (AIH11) | 13 | 47 | (AIL11) AI59 |

| AI12 (AIH12) | 14 | 48 | (AIL12) AI60 |

| AI13 (AIH13) | 15 | 49 | (AIL13) AI61 |

| AI14 (AIH14) | 16 | 50 | (AIL14) AI62 |

| AI15 (AIH15) | 17 | 51 | (AIL15) AI63 |

| AI16 (AIH16) | 18 | 52 | (AIL16) AI64 |

| AI17 (AIH17) | 19 | 53 | (AIL17) AI65 |

| AI18 (AIH18) | 20 | 54 | (AIL18) AI66 |

| AI19 (AIH19) | 21 | 55 | (AIL19) AI67 |

| AI20 (AIH20) | 22 | 56 | (AIL20) AI68 |

| AI21 (AIH21) | 23 | 57 | (AIL21) AI69 |

| AI22 (AIH22) | 24 | 58 | (AIL22) AI70 |

| AI23 (AIH23) | 25 | 59 | (AIL23) AI71 |

| AIGND        | 26 | 60 | AIGND        |

| AI24 (AIH24) | 27 | 61 | (AIL24) AI72 |

| AI25 (AIH25) | 28 | 62 | (AIL25) AI73 |

| AI26 (AIH26) | 29 | 63 | (AIL26) AI74 |

| AI27 (AIH27) | 30 | 64 | (AIL27) AI75 |

| AI28 (AIH28) | 31 | 65 | (AIL28) AI76 |

| AI29 (AIH29) | 32 | 66 | (AIL29) AI77 |

| AI30 (AIH30) | 33 | 67 | (AIL30) AI78 |

| AI31 (AIH31) | 34 | 68 | (AIL31) AI79 |

Table 3-2: CN1 Pin Assignment for PCI/PCIe/PXI-62208

\* Symbols in "()" are for differential mode connection.

## **CN2** Connector

| DA0OUT       | 1   | 35 | AOGND                        |

|--------------|-----|----|------------------------------|

| DAUCUT       | 2   | 36 | AOGND                        |

| AOEXTREF     | 3   | 37 | AOGND                        |

| NC           | 4   | 38 | NC                           |

| DGND         | 5   | 39 | DGND                         |

| EXTWFTRIG    | 6   | 40 | DGND                         |

| EXTDTRIG     | 7   | 40 | DGND                         |

| SSHOUT       | 8   | 41 | SDIO / DGND*                 |

| RESERVED     | 9   | 43 | SDIO / DGIND<br>SDI1 / DGND* |

| RESERVED     | 10  | 44 | SDI2 / DGND*                 |

| AFI1         | 10  | 44 | SDI2 / DGIND<br>SDI3 / DGND* |

| AFIO         | 11  | 45 | DGND                         |

| GPTC0 SRC    | 12  | 40 | DGND                         |

| GPTC0 GATE   | 14  | 48 | DGND                         |

| GPTC0 UPDOWN | 14  | 49 | DGND                         |

| GPTC0_OFDOWN | 16  | 50 | DGND                         |

| GPTC1 SRC    | 10  | 51 | DGND                         |

| GPTC1 GATE   | 18  | 52 | DGND                         |

| GPTC1 UPDOWN | 19  | 53 | DGND                         |

| GPTC1 OUT    | 20  | 54 |                              |

| EXTTIMEBASE  | 20  | 55 | DGND                         |

| PB7          | 22  | 56 | PB6                          |

| PB5          | 23  | 57 | PB4                          |

| PB3          | 24  | 58 | PB2                          |

| PB1          | 25  | 59 | PBO                          |

| PC7          | 26  | 60 | PC6                          |

| PC5          | 27  | 61 | PC4                          |

| DGND         | 28  | 62 | DGND                         |

| PC3          | 29  | 63 | PC2                          |

| PC1          | 30  | 64 | PCO                          |

| PA7          | 31  | 65 | PA6                          |

| PA5          | 32  | 66 | PA4                          |

| PA3          | 33  | 67 | PA2                          |

| PA1          | 34  | 68 | PAO                          |

| .,,1         | - · |    |                              |

## Table 3-3: CN2 Pin Assignment for PCI/PCIe/PXI-62204/62205/62206

\*Pin 42~45 are SDI<0.3> for PCI/PCIe/PXI-62204; DGND for PCI/PCIe/PXI-62205/62206

| AI32 (AIH32) | 1  | 35 | (AIL32) AI80 |

|--------------|----|----|--------------|

| AI33 (AIH33) | 2  | 36 | (AIL33) AI81 |

| AI34 (AIH34) | 3  | 37 | (AIL34) AI82 |

| AI35 (AIH35) | 4  | 38 | (AIL35) AI83 |

| AI36 (AIH36) | 5  | 39 | (AIL36) AI84 |

| AI37 (AIH37) | 6  | 40 | (AIL37) AI85 |

| AI38 (AIH38) | 7  | 41 | (AIL38) AI86 |

| AI39 (AIH39) | 8  | 42 | (AIL39) AI87 |

| EXTATRIG     | 9  | 43 | AIGND        |

| AI40 (AIH40) | 10 | 44 | (AIL40) AI88 |

| AI41 (AIH41) | 11 | 45 | (AIL41) AI89 |

| AI42 (AIH42) | 12 | 46 | (AIL42) AI90 |

| AI43 (AIH43) | 13 | 47 | (AIL43) AI91 |

| AI44 (AIH44) | 14 | 48 | (AIL44) AI92 |

| AI45 (AIH45) | 15 | 49 | (AIL45) AI93 |

| AI46 (AIH46) | 16 | 50 | (AIL46) AI94 |

| AI47 (AIH47) | 17 | 51 | (AIL47) AI95 |

| AIGND        | 18 | 52 | AIGND        |

| NC           | 19 | 53 | NC           |

| EXTDTRIG     | 20 | 54 | AFIO         |

| EXTTIMEBASE  | 21 | 55 | DGND         |

| PB7          | 22 | 56 | PB6          |

| PB5          | 23 | 57 | PB4          |

| PB3          | 24 | 58 | PB2          |

| PB1          | 25 | 59 | PB0          |

| PC7          | 26 | 60 | PC6          |

| PC5          | 27 | 61 | PC4          |

| DGND         | 28 | 62 | DGND         |

| PC3          | 29 | 63 | PC2          |

| PC1          | 30 | 64 | PC0          |

| PA7          | 31 | 65 | PA6          |

| PA5          | 32 | 66 | PA4          |

| PA3          | 33 | 67 | PA2          |

| PA1          | 34 | 68 | PA0          |

Table 3-4: CN2 Pin Assignment for PCI/PCIe/PXI-62208

## **CN1/CN2** Connector Signal Description

| Signal Name                 | Reference | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------|-----------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AIGND                       | _         | _         | Analog ground for AI. All three<br>ground references (AIGND, AOGND,<br>and DGND) are connected together<br>on board.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| AI<063/95>                  | AIGND     | Input     | <ul> <li>For PCI/PCIe/PXI-62204/62205/<br/>62206: Analog Input Channels<br/>0~63. Each channel pair, AI<i,<br>i+32&gt; (I=031) can be configured<br/>either two single-ended inputs or<br/>one differential input pair(marked<br/>as AIH&lt;031&gt; and AIL&lt;031&gt;).</i,<br></li> <li>For PCI/PCIe/PXI-62208: Analog<br/>Input Channels 0~95. Each channel<br/>pair, AI<i, i+48=""> (I=037) can be<br/>configured either two single-<br/>ended inputs or one differential<br/>input pair(marked as AIH&lt;047&gt;<br/>and AIL&lt;047&gt;).</i,></li> </ul> |

| AISENSE                     | AIGND     | Input     | Analog Input Sense. This pin is the reference for any channels AI<063> in NRSE input configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EXTATRIG                    | AIGND     | Input     | External AI analog trigger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DA0OUT                      | AOGND     | Output    | AO channel 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DA1OUT                      | AOGND     | Output    | AO channel 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| AOEXTREF                    | AOGND     | Input     | External reference for AO channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| AOGND                       | _         | _         | Analog ground for AO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| EXTWFTRIG                   | DGND      | Input     | External AO waveform trigger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| EXTDTRIG                    | DGND      | Input     | External AI digital trigger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RESERVED                    | _         | Output    | Reserved. Please leave it open                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SDI<03><br>(for 62204 only) | DGND      | Input     | Synchronous digital inputs. These 4<br>digital inputs are sampled<br>simultaneously with the analog signal<br>input.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| GPTC<0,1>_SRC               | DGND      | Input     | Source of GPTC<0,1>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| GPTC<0,1>_GATE              | DGND      | Input     | Gate of GPTC<0,1>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Table | 3-5: | CN1/CN2 | Signal | Description |

|-------|------|---------|--------|-------------|

|-------|------|---------|--------|-------------|

| Signal Name      | Reference | Direction | Description                                      |

|------------------|-----------|-----------|--------------------------------------------------|

| GPTC<0,1>_OUT    | DGND      | Input     | Output of GPTC<0,1>                              |

| GPTC<0,1>_UPDOWN | DGND      | Input     | Up/Down of GPTC<0,1>                             |

| EXTTIMEBASE      | DGND      | Input     | External Timebase                                |

| DGND             | _         | _         | Digital ground                                   |

| PB<7,0>          | DGND      | PIO*      | Programmable DIO of 8255 Port B                  |

| PC<7,0>          | DGND      | PIO*      | Programmable DIO of 8255 Port C                  |

| PA<7,0>          | DGND      | PIO*      | Programmable DIO of 8255 Port A                  |

| AFIO             | DGND      | Input     | Auxiliary Function Input 0 (ADCONV,<br>AD_START) |

| AFI1             | DGND      | Input     | Auxiliary Function Input 1 (DAWR, DA_START)      |

Table 3-5: CN1/CN2 Signal Description

## **SSI Connector**

| -                       |    |    |      |

|-------------------------|----|----|------|

| SSI_TIMEBASE            | 1  | 2  | DGND |

| SSI_ADCONV              | 3  | 4  | DGND |

| SSI_DAWR / RESERVED*    | 5  | 6  | DGND |

| SSI_SCAN_START          | 7  | 8  | DGND |

| RESERVED                | 9  | 10 | DGND |

| SSI_AD_TRIG             | 11 | 12 | DGND |

| SSI_DA_TRIG / RESERVED* | 13 | 14 | DGND |

| RESERVED                | 15 | 16 | DGND |

| RESERVED                | 17 | 18 | DGND |

| RESERVED                | 19 | 20 | DGND |

|                         |    |    |      |

Table 3-6: SSI Connector Pin Assignment

\*Pin 5 and 13 are reserved for PCI/PXI-62208.

## SSI Connector Signal Description:

| SSI Timing Signal | Setting | Function                                                                |

|-------------------|---------|-------------------------------------------------------------------------|

|                   | Master  | Send the TIMEBASE out                                                   |

| SSI_TIMEBASE      | Slave   | Accept the SSI_TIMEBASE to replace the internal TIMEBASE signal.        |

|                   | Master  | Send the ADCONV out                                                     |

| SSI_ADCONV        | Slave   | Accept the SSI_ADCONV to replace the internal ADCONV signal.            |

|                   | Master  | Send the SCAN_START out                                                 |

| SSI_SCAN_START    | Slave   | Accept the SSI_SCAN_START to replace the internal<br>SCAN_START signal. |

|                   | Master  | Send the internal AD_TRIG out                                           |

| SSI_AD_TRIG       | Slave   | Accept the SSI_AD_TRIG as the digital trigger signal.                   |

|                   | Master  | Send the DAWR out.                                                      |

| SSI_DAWR          | Slave   | Accept the SSI_DAWR to replace the internal DAWR signal.                |

|                   | Master  | Send the DA_TRIG out.                                                   |

| SSI_DA_TRIG       | Slave   | Accept the SSI_DA_TRIG as the digital trigger signal.                   |

Table 3-7: SSI Connector Legend

## 3.2 Analog Input Signal Connection

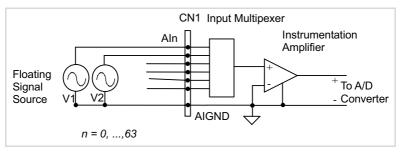

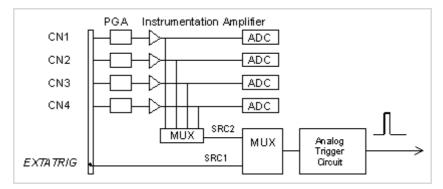

The PCI/PCIe/PXI-62204/62205/62206/62208 card provides up to 64 single-ended or 32 differential analog input channels. You can fill the Channel Gain Queue to get desired combination of the input signal types. The analog signal can be converted to digital values by the A/D converter. To avoid ground loops and get more accurate measurements from the A/D conversion, it is important to understand the signal source type and how to connect the analog input signals.

### **Types of signal sources**

#### **Floating Signal Sources**

A floating signal source means it is not connected in any way to the buildings ground system. A device with an isolated output is a floating signal source, such as optical isolator outputs, transformer outputs, and thermocouples.

#### **Ground-Referenced Signal Sources**

A ground-referenced signal means it is connected in some way to the building system. That is, the signal source is already connected to a common ground point with respect to the PCI/PCIe/PXI-62204/ 62205/62206/62208 card, assuming that the computer is plugged into the same power system. Non-isolated out-puts of instruments and devices that plug into the buildings power system are ground-referenced signal sources.

### **Input Configurations**

#### **Single-Ended Connections**

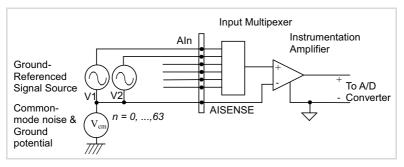

A single-ended connection is used when the analog input signal is referenced to a ground that can be shared with other analog input signals. There are two types of single-ended connections: RSE and NRSE. In RSE configuration, the PCI/PCIe/PXI-62204/62205/62206/62208 card provides the grounding point for the external analog input signals and is suitable for floating signal sources. In the NRSE configuration the board does not provide the grounding point, the external analog input signal provides its own reference grounding point and is suitable for ground-referenced signals.

Referenced Single-ended (RSE) Mode

In referenced single-ended mode, all input signals are connected to the ground provided by the PCI/PCIe/PXI-62204/62205/62206/62208 card. This is suitable for connections with floating signal sources. Figure 3-1 shows an illustration. Note that when more than two floating sources are connected, these sources will be referenced to the same common ground.

Figure 3-1: Floating Source and RSE Input Connections

Non-Referenced Single-ended (NRSE) Mode

To measure ground-referenced signal sources, which are connected to the same ground point, you can connect the signals in NRSE mode. Figure 3-2 illustrates the connection. The signals local ground reference is connected to the negative input of the instrumentation Amplifier (AISENSE pin on CN1 connector), and the common-mode ground potential between signal ground and the ground on board will be rejected by the instrumentation amplifier.

Figure 3-2: Ground-referenced Sources and NRSE Input Connections

## **Differential Input Mode**

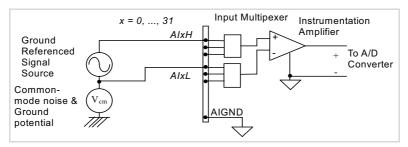

The differential input mode provides two inputs that respond to signal voltage difference between them. If the signal source is ground-referenced, the differential mode can be used for the common-mode noise rejection. Figure 3-3 shows the connection of ground-referenced signal sources under differential input mode.

Figure 3-3: Ground-referenced Source and Differential Input

#### **Ground-referenced Source and Differential Input**

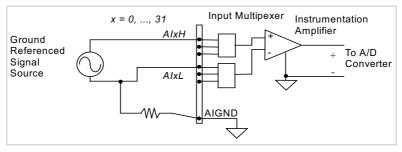

Figure 3-4 shows how to connect a floating signal source to the PCI/ PCIe/PXI-62204/62205/62206/62208 card in differential input mode. For floating signal sources, you need to add a resistor at each channel to provide a bias return path. The resistor value should be about 100 times the equivalent source impedance. If the source impedance is less than 100ohms, you can simply connect the negative side of the signal to AIGND as well as the negative input of the Instrumentation Amplifier without any resistors. In differential input mode, less noise couples into the signal connections than in single-ended mode.

Figure 3-4: Floating Source and Differential Input

# 4 Operation Theory

The operation theory of the PCI/PCIe/PXI-62204/62205/62206/62208 card functions are described in this chapter. The functions include the A/D conversion, D/A conversion, digital I/O, and general purpose counter/timer. The operation theory can help you understand how to configure and program the PCI/PCIe/PXI-62204/62205/62206/62208 card.

# 4.1 A/D Conversion

When using an A/D converter, you must know about the properties of the signal to be measured. You may decide which channel to use and how to connect the signals to the card. In addition, users should define and control the A/D signal configurations, including channels, gains, and polarities (unipolar/bipolar).

The A/D acquisition is initiated by a trigger source and you must decide how to trigger the A/D conversion. The data acquisition will start once a trigger condition is matched.

After the end of an A/D conversion, the A/D data is buffered in a Data FIFO. The A/D data can now be transferred into the system memory for further processing.

# PCI/PCIe/PXI-62204/62208 AI Data Format

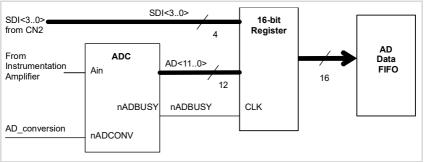

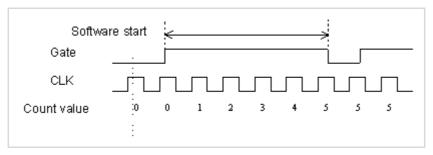

# Synchronous Digital Inputs (PCI/PCIe/PXI-62204 only)

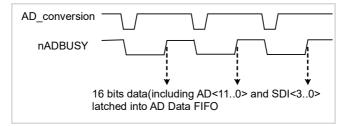

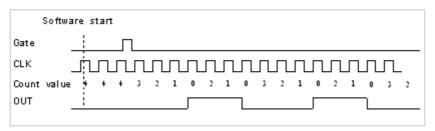

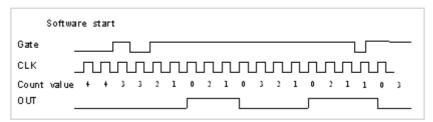

When each A/D conversion is completed, the 14-bits converted digital data accompanied with 2 bits of SDI<1..0>\_X per channel from J5 will be latched into the 16-bit register and data FIFO as shown in Figure 4-1 and Figure 4-2. Therefore, you can simultaneously sample one analog signal with four digital signals. The data format of every acquired 16-bit data is as follows:

D11, D10, D9 ...... D1, D0, b3, b2, b1, b0 Where D11, D10, D9 ...... D1, D0: 2's complement A/D 12-bit data b3, b2, b1, b0: Synchronous Digital Inputs SDI<3..0>

Figure 4-1: Synchronous Digital Inputs Block Diagram

Figure 4-2: Synchronous Digital Inputs Timing

**NOTE** Since the analog signal is sampled when an A/D conversion starts (falling edge of A/D\_conversion signal), while SDI<3..0> are sampled right after an A/D conversion completes (rising edge of nADBUSY signal). Precisely SDI<3..0> are sampled with 280ns lag to the analog signal.

Table 4-1 and Table 4-2 illustrate the ideal transfer characteristics of various input ranges of the PCI/PCIe/PXI-62204/62205/62206/62208 card.

| Description           | Bipolar Analog Input Range |         |         | Digital<br>code |      |

|-----------------------|----------------------------|---------|---------|-----------------|------|

| Full-scale Range      | ±10V                       | ±5V     | ±2.5V   | ±1.25V          | _    |

| Least significant bit | 4.88mV                     | 2.44mV  | 1.22mV  | 0.61mV          | -    |

| FSR-1LSB              | 9.9951V                    | 4.9976V | 2.4988V | 1.2494V         | 7FFX |

| Midscale +1LSB        | 4.88mV                     | 2.44mV  | 1.22mV  | 0.61mV          | 001X |

| Midscale              | 0V                         | 0V      | 0V      | 0V              | 000X |

| Midscale –1LSB        | -4.88mV                    | -2.44mV | -1.22mV | -0.61mV         | FFFX |

| -FSR                  | -10V                       | -5V     | -2.5V   | -1.25V          | 800X |

Table 4-1: Bipolar Analog Input Range and Output Digital Code on PCI/PCIe/PXI-62204/62208

Note that the last 4 digital codes are SDI<3..0> and is supported only on PCI/PCIe/PXI-62204)

| Description           | Unipol    | Digital code |            |      |

|-----------------------|-----------|--------------|------------|------|

| Full-scale Range      | 0V to 10V | 0 to +5V     | 0 to +2.5V | —    |

| Least significant bit | 2.44mV    | 1.22mV       | 0.61mV     | —    |

| FSR-1LSB              | 9.9976V   | 4.9988V      | 2.9994V    | 7FFX |

| Midscale +1LSB        | 5.00244V  | 2.50122V     | 1.25061V   | 001X |

| Midscale              | 5V        | 2.5V         | 1.25V      | 000X |

| Midscale –1LSB        | 4.9976V   | 2.4988V      | 1.2494V    | FFFX |

| -FSR                  | 0V        | 0V           | 0V         | 800X |

Table

4-2: Unipolar Analog Input Range and Output Digital Code on PCI/PCIe/PXI-62204/62208

Note that the last 4 digital codes are SDI<3..0> and is supported only on PCI/PCIe/PXI-62204.

# PCI/PCIe/PXI-62205/62206 AI Data Format

The data format of the acquired 16-bit A/D data is **2's Complement coding**. Table 4-3 and Table 4-4 illustrate the valid input ranges and the ideal transfer characteristics.

| Description           | Bipolar Analog Input Range |           |           | Digital code |      |

|-----------------------|----------------------------|-----------|-----------|--------------|------|

| Full-scale Range      | ±10V                       | ±5V       | ±2.5V     | ±1.25V       | —    |

| Least significant bit | 305.2 μV                   | 152.6 μV  | 76.3 μV   | 38.15 μV     | _    |

| FSR-1LSB              | 9.999695V                  | 4.999847V | 2.499924V | 1.249962V    | 7FFF |

| Midscale +1LSB        | 305.2 μV                   | 152.6 μV  | 76.3 μV   | 38.15 μV     | 0001 |

| Midscale              | 0V                         | 0V        | 0V        | 0V           | 0000 |

| Midscale -1LSB        | -305.2 μV                  | -152.6 μV | -76.3 μV  | -38.15 μV    | FFFF |

| -FSR                  | -10V                       | -5V       | -2.5V     | -1.25V       | 8000 |

Table 4-3: Bipolar Analog Input Range and Output Digital Code for PCI/PCIe/PXI-62205/

62206

| Description           | Unipolar Analog Input Range |           |            | Digital code |      |

|-----------------------|-----------------------------|-----------|------------|--------------|------|

| Full-scale Range      | 0V to 10V                   | 0 to +5V  | 0 to +2.5V | 0 to +1.25V  | -    |

| Least significant bit | 152.6 μV                    | 76.3 μV   | 38.15 μV   | 19.07 μV     | —    |

| FSR-1LSB              | 9.999847V                   | 4.999924V | 2.499962V  | 1.249981V    | 7FFF |

| Midscale +1LSB        | 5.000153V                   | 2.500076V | 1.250038V  | 0.625019V    | 0001 |

| Midscale              | 5V                          | 2.5V      | 1.25V      | 0.625V       | 0000 |

| Midscale -1LSB        | 4.999847V                   | 2.499924V | 1.249962V  | 0.624981V    | FFFF |

Table

4-4: Unipolar Analog Input Range and Output Digital Code for PCI/PCIe/PXI-62205/

62206

# Software Conversion with Polling Data Transfer Acquisition Mode (Software Polling)

This is the easiest way to acquire a single A/D data. The A/D converter starts one conversion whenever the dedicated software command is executed. Then the software would poll the conversion status and read the A/D data back when it is available.

This method is very suitable for applications that needs to process A/D data in real time. Under this mode, the timing of the A/D conversion is fully controlled by the software. However, it is difficult to control the A/D conversion rate.

# Specifying Channel, Gain, and Input Configurations in the Channel Gain Queue

In Software Polling and Programmable Scan Acquisition mode, the channel, gain, polarity, and input configuration (RSE, NRSE, or DIFF) can be specified in the Channel Gain Queue. You can fill the channel number in the Channel Gain Queue in any order. The channel order of acquisition will be the same as the order you set in the Channel Gain Queue. Therefore, you can acquire data with user-defined channel orders and with different settings on each channel.

When the specified channels have been sampled from the first data to the last data in the Channel Gain Queue, the settings in Channel Gain Queue are maintained. You do not need to re-configure the Channel Gain Queue if you want to keep on sampling data in the same order. The maximum number of entries you can set in the Channel Gain Queue is 512.

Example:

First you can set entries in Channel Gain Queue:

- ▶ Ch3 with bipolar ±10V, RSE connection

- ▶ Ch1 with bipolar ±2.5V, DIFF connection

- ▶ Ch2 with unipolar 5V, NRSE connection

- ▶ Ch1 with bipolar ±2.5V, DIFF connection

If you read 10 data by software polling method, then the acquisition sequence of channels is 3, 1, 2, 1, 3, 1, 2, 1, 3, 1.

# Programmable Scan Acquisition Mode

# Scan Timing and Procedure

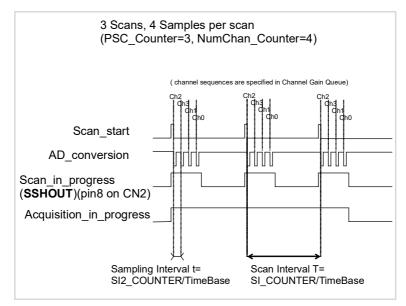

It is recommended that you use this mode if your applications need a fixed and precise A/D sampling rate. You can accurately program the period between conversions of individual channels. There are at least four counters which need to be specified:

- SI\_counter (24-bit): Specify the Scan Interval = SI\_counter / Timebase

- SI2\_counter (16-bit): Specify the data Sampling Interval = SI2\_counter/Timebase

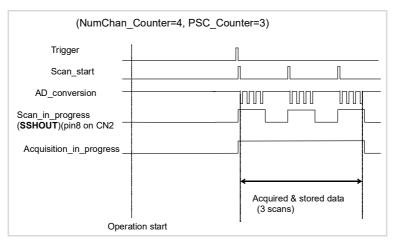

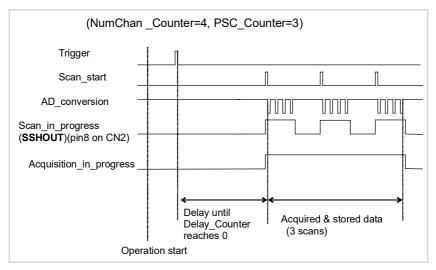

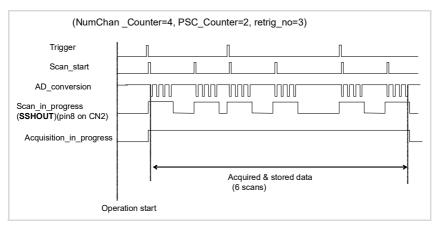

- PSC\_counter (24-bit): Specify Post Scan Counts after a trigger event

- NumChan\_counter (9-bit): Specify the number of samples per scan

The acquisition timing and the meanings of the 2 counters are illustrated in Figure 4-3.

# **TIMEBASE Clock Source**

In scan acquisition mode, all the A/D conversions start on the output of counters, which use TIMEBASE as the clock source. By software you can specify the TIMEBASE to be either an internal clock source (onboard 40 MHz clock) or an external clock input (EXTTIMEBASE) on CN2 connector. The external TIMEBASE is useful when you want to acquire data at rates not available with the internal A/D sample clock. The external clock source should generate TTL-compatible continuous clocks and with a maximum frequency of 40 MHz while the minimum should be 1 MHz. Refer to section 4.6 for information on user-controllable timing signals.

Figure 4-3: Scan Timing

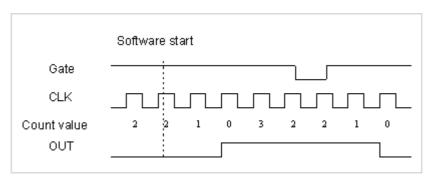

There are four trigger modes to start the scan acquisition. Refer to section 4.1 for details. The data transfer mode is discussed in the following section.